- program - binarny wykonywalny plik musi być wprowadzony do pamięci operacyjnej i rozpatrywany jako proces

- zbiór procesów czekających na dysku na wprowadzenie do pamięci w celu wykonania tworzy kolejkę wejściową

- zanim program zostanie wykonany, przechodzi on przez kilka faz

rys.8.1 Wieloetapowe przetwarzanie programu użytkownika

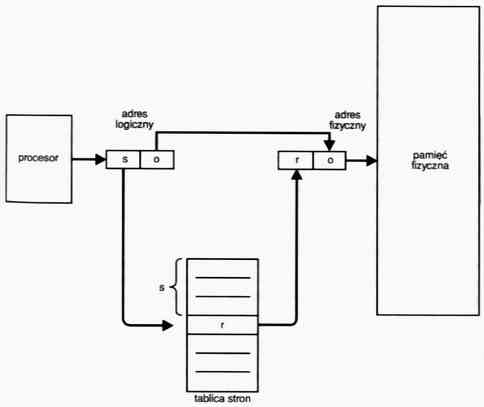

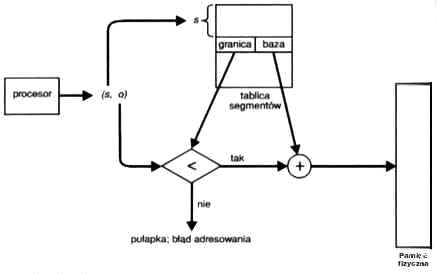

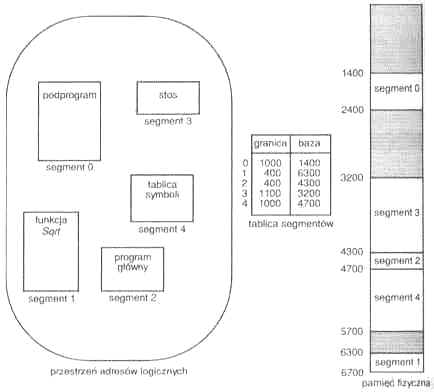

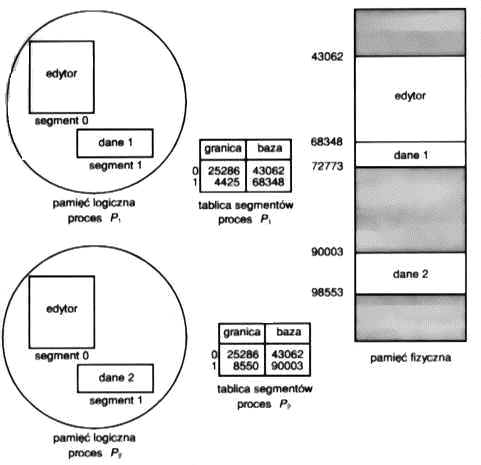

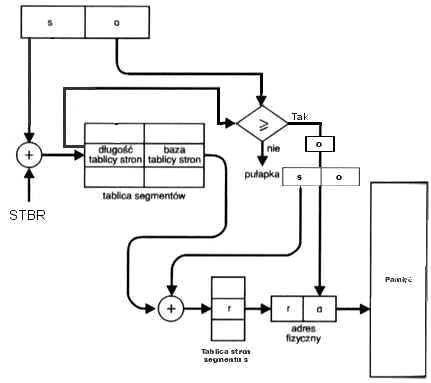

- Wiązanie adresów

- podczas faz przetwarzania programu, reprezentacja adresów pamięci komputera może ulegać zmianom

- w programie źródłowym adresy są wyrażone w sposób symboliczny, (np. LICZNIK)

- kompilator na ogół wiąże te adresy z adresami względnymi (np. "14 bajtów licząc od początku danego modułu")

- konsolidator lub program ładujący powiąże dalej te adresy względne z adresami bezwzględnymi (np. 74014)

- powiązanie rozkazów i danych z adresami pamięci może w zasadzie zostać wykonane w dowolnym z poniższych kroków.

- czas kompilacji: jeśli podczas kompilacji jest znane miejsce, w którym proces będzie wykonywany, to można wygenerować kod bezwzględny; kod trzeba skompilować od nowa, gdy w późniejszym czasie ulegnie zmianie adres początkowy programu

- czas ładowania: jeśli podczas kompilacji nie wiadomo, gdzie będzie umieszczony proces, to kompilator wytworzy kod przemieszczalny; ostateczne wiązanie jest opóźniane do czasu ładowania

- czas wykonania: jeśli proces może ulegać przemieszczeniom w pamięci podczas swojego wykonania, to trzeba zaczekać z wiązaniem adresów aż do czasu wykonywania; wymaga to specjalnego sprzętu

- Ładowanie dynamiczne

- podprogram nie jest wprowadzany do pamięci dopóty, dopóki nie zostanie wywołany

- umożliwia to lepsze wykorzystanie pamięci; podprogram nieużywany nigdy nie będzie załadowany

- schemat jest szczególnie przydatny wtedy, kiedy okazjonalnie trzeba wykonywać wielkie fragmenty kodu

- nie jest wymagane specjalne wsparcie ze strony SO; to użytkownicy są odpowiedzialni za takie zaprojektowanie programów, aby mogły korzystać z metody

- Konsolidacja dynamiczna

- konsolidacja jest opóźniana do czasu wykonania programu

- w obrazie binarnym, w miejscu odwołania bibliotecznego znajduje się tylko namiastka procedury, wskazująca jak odnaleźć odpowiedni podprogram biblioteki

- namiastka procedury wprowadza na swoje miejsca adres potrzebny podprogramowi i powoduje jego wykonanie

- SO musi sprawdzić, czy potrzebny podprogram znajduje się w obszarze pamięci innych procesów

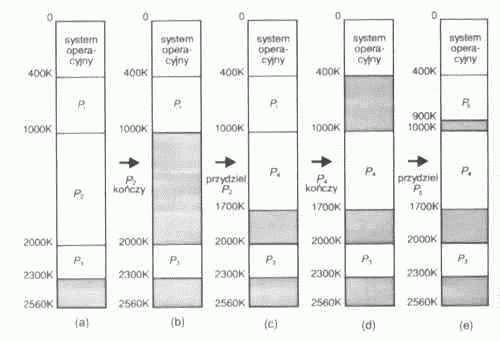

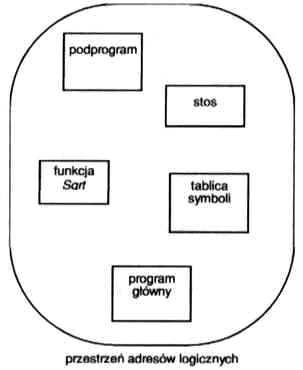

- Nakładki

- trzymaj w pamięci tylko te rozkazy i dane, które są stale potrzebne

- ta technika może być stosowana gdy proces jest większy aniżeli ilość przydzielonej mu pamięci

- np. mamy dwuprzebiegowy asembler:

- w pierwszym przebiegu konstruuje on tablicę symboli

- w drugim, generuje kod maszynowy

- taki asembler można podzielić na kod przebiegu 1, kod przebiegu 2, tablicę symboli i wspólne podprogramy

- do załadowania wszystkiego, potrzeba by było 200kB pamięci, a mamy tylko 150kB

Rys. 8.2 Nakładki dwuprzebiegowego asemblera

- definiujemy 2 nakładki:

- A - złożoną z tablicy symboli, wspólnych podprogramów i kodu przebiegu 1

- B - złożoną z tablicy symboli, wspólnych podprogramów i kodu przebiegu 2

- dodajmy moduł obsługi nakładek i rozpoczynamy od wykonania nakładki A

- nakładki nie wymagają specjalnego wsparcia SO, są wykonane przez użytkownika